本征半导体硅(纯度99.999999999%)和锗的导电性能不好,通过加入杂质可以改善其导电性能。

在纯净的硅中加入5价杂质,形成n(negative)型半导体。

在纯净的硅中加入3价杂质,形成p(positive)型半导体。

将两种材料合在一起,则在它们交界处就会形成pn结。

2.2.1 掺杂

掺杂可以增加载流子(电子和空穴)的数量,低电阻率和导电性能。

加入5价电子元素材料,形成n型半导体。在n型半导体材料中,自由电子称为多数载流子;空穴为少数载流子

加入3价电子元素材料,形成p型半导体。在p型半导体材料中,空穴称为多数载流子;自由电子为少数载流子

2.2.2 pn结

在一块本征硅上参杂,使得硅的一半形成

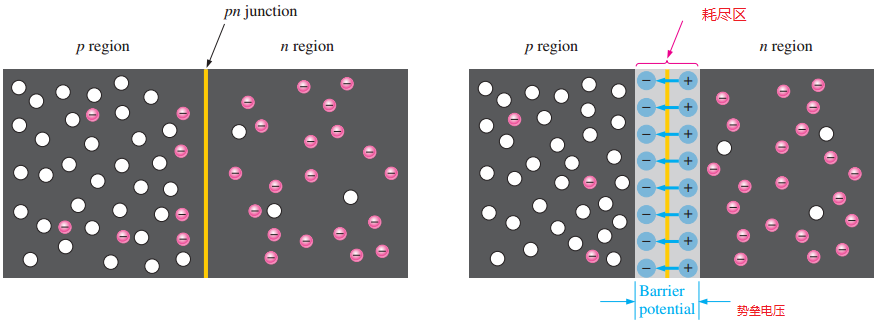

在一块本征硅上参杂,使得硅的一半形成n型半导体,另一半形成p型半导体,则在交界处会形成pn结。在n区有很多自由电子(多数载流子)和少量由热激发产生的空穴(少数载流子)。在p区有很多空穴(多数载流子)和少量由热激发产生的自由电子(少数载流子)。pn结形成了基本的二极管,它是所有固态半导体器件的工作基础。二极管是一种只允许电流朝一个方向流动的器件。

耗尽区当pn结形成之后,在结附近的一些导带电子漂移到区并且和区的空穴复合,如图2-5a所示。每个电子穿过结并且和空穴复合后,在n区靠近结处会留下带一个净正电荷的五价原子。同样,当电子和p区的一个空穴复合,一个3价原子会带一个净负电荷。因此,结的n区会有正离子,区会有负离子。正负离子出现在结的相对一侧,在耗尽区处产生势垒电压(V)。势垒电压的大小受温度影响。在室温下,一般硅大约为0.7V,锗为0.3V。因为二极管很少使用,所以在实际应用中势电压为0.7V,本书内容也假设势电压为0.7V。

为了扩散到p区,n区的导带电子必须克服所有正离子的吸力和负离子的力。在离子层形成后,结两边的区域中自由电子和空穴的数量会急剧减少,这个区域称为耗尽区,如图2-5b所示。电荷穿过交界处的任何运动都需要克服势垒电压。