本节将介绍 JFET 是如何作为电压控制、恒流器件工作的,也将讨论漏极特性曲线和跨导曲线,以及 JFET 的截止、夹断与 JFET 的输入电阻和电容等内容。

学完本节后,你应该掌握以下内容:

- 描述结型场效应管(JFET)的结构和工作原理

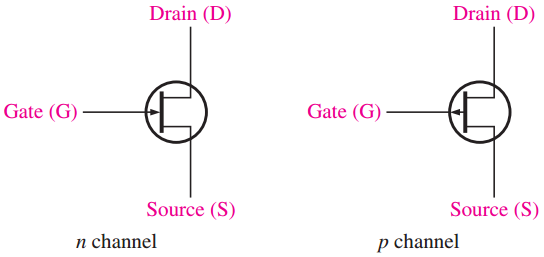

- 画出 n 沟道或 p 沟道 JFET 的符号

- 解释 JFET 的漏极特性曲线,包括可变电阻区和恒流区

- 解释参数 $g_m、I_{DSS} 、I_{GSS} 、C_{iss} 、V_{GS(off)}和 V_P$

- 描述 JFET 的跨导曲线并且解释它与漏极特性曲线的关系

4.2.1 JFET 工作原理

$$

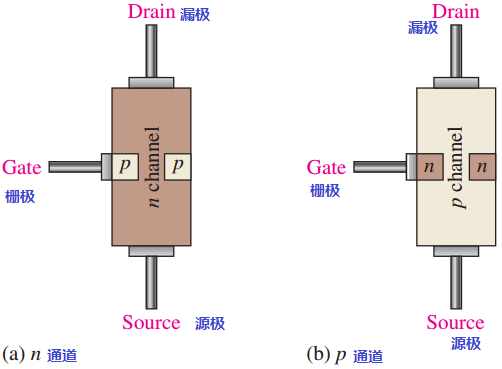

a) n沟道~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)p沟道

$$

$$

a) n沟道~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)p沟道

$$

$$

图4-2~~~~~两种JFET的基本结构

$$

图4-2a给出了 n 沟道结型场效应管(JFET)的基本结构。电线连接到 n 沟道的两端,在图4-2中漏极位于上端,源极位于下端。沟道是一个导体: 对 n 沟道 JFET 而言,电子是载流子;对 p 沟道 JFET 而言,空穴是载流子。在没有外加电压的情况下,沟道在两个方向都能导通电流。

在 n 沟道器件中,将 p 型材料掺杂到 n 沟道中来形成 pn 结,并连接到栅极。图 4-2a 显示的是将 p 型材料掺杂进两个区域,这两个区域一般由制造商在内部进行连接形成单个栅极。(一种专用JFET,也称为双栅 JFET,有独立的电极连接到两个区域。)在结构图中,为了简单起见,两个 p 型区域之间的连接被省略掉,只给出到其中一个区域的连接。图4-2b给出了力沟道 JFET。

如前所述,JFET 中的沟道是栅极和源极之间的一个窄导电通路。沟道的宽度, 也就是沟道的导电能力,是由栅极电压控制的。当没有栅极电压时,沟道能通过最大的电流。当栅极施加反向偏置时,沟道宽度变窄,导电能力下降。

$$

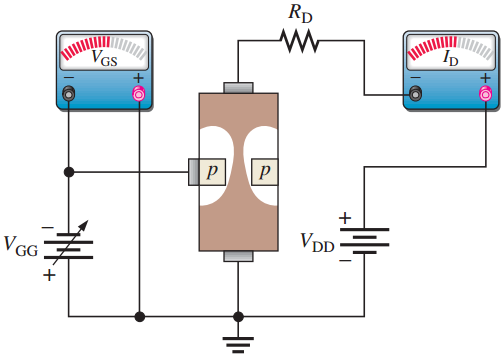

a)~~~JFET的导通偏置

$$

为了说明上述过程,在一个 n 沟道器件上加上一个一般的工作电压,如图4-3a所示。$V_{DD}$ 提供了一个正的漏源电压,使电子由源极向漏极流动。对 N 沟道 JFET 而言,栅源结的反向偏置由

$$

a)~~~JFET的导通偏置

$$

为了说明上述过程,在一个 n 沟道器件上加上一个一般的工作电压,如图4-3a所示。$V_{DD}$ 提供了一个正的漏源电压,使电子由源极向漏极流动。对 N 沟道 JFET 而言,栅源结的反向偏置由负的栅极电压实现。如图4-3所示,$V_{GG}$ 设置了栅极与源极之间的反向偏置电压。注意,FET 中没有任何正向偏置的 pn 结; 这也是 FET 和 BJT 的主要区别之一。

$$

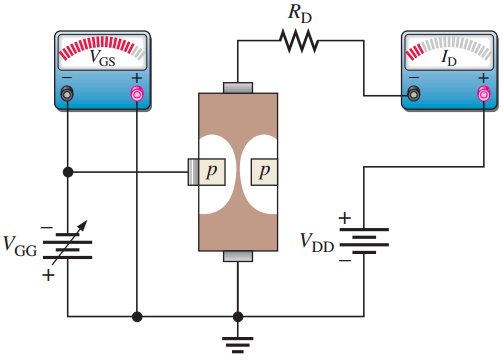

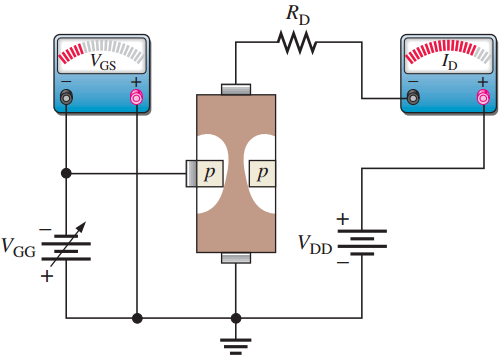

b)~~V_{GG}增大将使沟道(白色区域之间)变窄,从而使沟道电阻增大,I_D 减小

$$

$$

b)~~V_{GG}增大将使沟道(白色区域之间)变窄,从而使沟道电阻增大,I_D 减小

$$

$$

c)~~V_{GG} 减小将使沟道(白色区域之间)变宽,从而使沟道电阻减小,I_D 增大

$$

$$

c)~~V_{GG} 减小将使沟道(白色区域之间)变宽,从而使沟道电阻减小,I_D 增大

$$

$$ 图4-3~~V_{GG}对沟道宽度、电阻和漏极电流的影响(V_{GG}=V_{GS}) $$

通过改变栅极电压,可以控制沟道宽度和沟道电阻,从而控制漏极电流 $I_D$,这个概念在图 4-3b 和 c 中说明。其中,白色区域表示的是由反向偏置产生的耗尽区。在沟道的漏极一端,该区域更宽,因为栅极和漏极之间的反向偏置电压比栅极和源极之间的反向偏置电压更大。

4.2.2 JFET符号

$$ a)n沟道 b) p沟道 $$

$$ 图4-4~~JFET电路符号 $$ n 沟道和 p 沟道 JFET 的电路符号如图 4-4 所示。可以看到漏极上的箭头方向,对 n 沟道而言是“指向里”,对 p 沟道而肓是“指向外”。

4.2.3漏极特性曲线

FET 的漏极特性曲线是漏极电流 $I_D$ 对漏源电压 $V_{DS}$ 之间的关系曲线,和 BJT 的集电极电流 $I_C$ 对集电极发射极间电压 $V_{CE}$ 曲线相对应。但是 BJT 特性曲线和 FET 特性曲线之间有很多重要差别。由于 FET 是一个电压控制器件,因此 FET 特性曲线上的第三个变量($V_{GS}$)的单位是电压,而 BJT 中是电流($I_B$)。本节介绍 n 沟道器件的漏极特性。p 沟道器件工作原理相同,但是极性相反。通常来说,n 沟道 JFET 比对应的 p 沟道 JFET 具有更好的指标,因此前者更为流行。

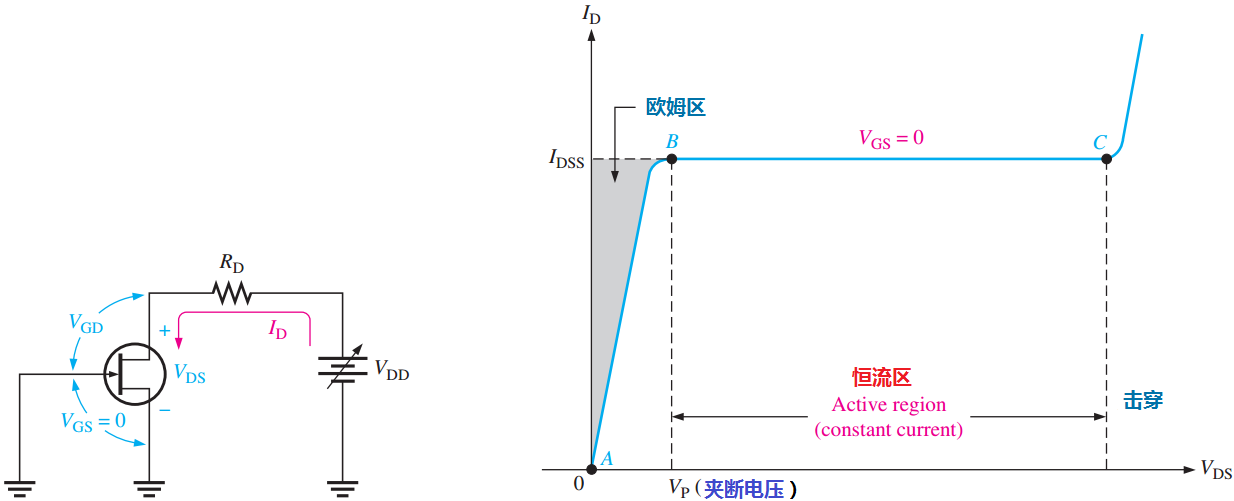

$$

a)在V_{GS}=0V,V_{DS} (V_{DD})变化的情况下JFET的工作~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

b)漏极特性

$$

$$

图4-5~~V_{GS}=0V时JFET的漏极特性曲线(其中给出了夹断电压)

$$

考虑 n 沟道 JFET 栅源电压为0($V_{GS} =0V$)的情况。0电压通过短接栅极和源极来实现,在图4-5a中,将栅极和源极都接地。随着 $V_{DD}$(此情况下也就是 $V_{DS}$)从 0V 开始增大,$I_D$ 也会相应增大,如图4-5b中 A 点和 B 点之间的曲线所示。在该区域中,沟道电阻基本是常数,因为耗尽区不大,不会产生较大的影响。该区域称为可变电阻区,因为 $V_{DS}$ 和 $I_D$ 之间的关系遵循欧姆定律。通过栅极电压可以改变电阻值的大小,因此可以将 JFET 作为电压控制的电阻使用。在后面的图 10-11(文氏桥)中给出了一个应用。更多应用可以参考配套实验练习手册中的实验14、15和27。

$$

a)在V_{GS}=0V,V_{DS} (V_{DD})变化的情况下JFET的工作~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

b)漏极特性

$$

$$

图4-5~~V_{GS}=0V时JFET的漏极特性曲线(其中给出了夹断电压)

$$

考虑 n 沟道 JFET 栅源电压为0($V_{GS} =0V$)的情况。0电压通过短接栅极和源极来实现,在图4-5a中,将栅极和源极都接地。随着 $V_{DD}$(此情况下也就是 $V_{DS}$)从 0V 开始增大,$I_D$ 也会相应增大,如图4-5b中 A 点和 B 点之间的曲线所示。在该区域中,沟道电阻基本是常数,因为耗尽区不大,不会产生较大的影响。该区域称为可变电阻区,因为 $V_{DS}$ 和 $I_D$ 之间的关系遵循欧姆定律。通过栅极电压可以改变电阻值的大小,因此可以将 JFET 作为电压控制的电阻使用。在后面的图 10-11(文氏桥)中给出了一个应用。更多应用可以参考配套实验练习手册中的实验14、15和27。

在图 4-5b 中的 B 点处,曲线变为水平,$I_D$ 开始基本保持不变。随着 $V_{DS}$ 从 B 点增大到 C 点,栅极到漏极之间的反向偏置电压($V_{GD}$)使得耗尽区变大到足以抵消 $V_{DS}$ 增大的影响,因此使 $I_D$ 基本不变。这一区域称为恒流区。

4.2.4夹断电压

当 $V_{GS} =0V$ 时,$I_D$变为几乎恒定(图4-5b中曲线上的 B 点)时,对应的 $V_{DS}$ 的值称为夹断电压,$V_P$. 注意,对于 n 沟道 JFET 而言,夹断电压为正值。对于给定的 JFET,$V_P$ 为确定的值。可以看出,当 $V_{DS}$ 超过夹断电压并继续增大时,对应的漏极电流几乎为常数。该漏极电流值为 $I_{DSS}$(栅极短路时漏极到源极电流),通常会在 JFET 的数据手册中给出。$I_{DSS}$ 是给定的 JFET 能够产生的最大漏极电流,与外部电路无关,并始终在 $V_{GS}=0V$ 的条件下确定。

继续分析图4-5b,在 C 点会发生击穿,此时对于 $V_{DS}$ 的任何进一步增加,$I_D$ 开始快速增大。因为击穿可能会造成器件不可逆的损坏,所以 JFET 通常工作在击穿以下区域,并通常在恒流区内(图4-5b中的 B 点和 C 点之间)工作。因此恒流区也被称为工作区。

4.2.5 $V_{GS}$控制 I_D

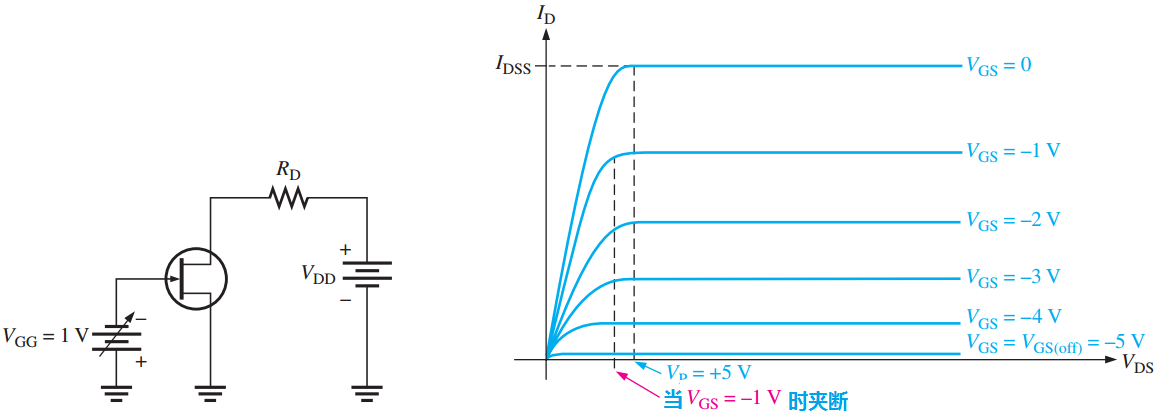

$$

a)JFET偏置在 V_{GS}=-1V~~~~~~~~~~~~~~~~~~~~~~~~

b)漏极特性曲线族

$$

在栅极与源极之间连接上一个偏置电压 $V_{GG}$,如图 4-6a 所示。通过调整 $V_{GG}$,使 $V_{GS}$ 往负值增大,可以得到如图 4-6b 所示的一族漏极特性曲线。注意,随着 $V_{GS}$ 变为更大的负值,$I_D$减小,因为沟道变窄。也可以看到对于每一组 $V_{GS}$ ,JFET 在小于 $V_P$ 的 $V_{DS}$ 值下达到夹断状态(恒流开始的位置)。由此可见,$V_{GS}$可以控制漏极电流的大小。

$$

a)JFET偏置在 V_{GS}=-1V~~~~~~~~~~~~~~~~~~~~~~~~

b)漏极特性曲线族

$$

在栅极与源极之间连接上一个偏置电压 $V_{GG}$,如图 4-6a 所示。通过调整 $V_{GG}$,使 $V_{GS}$ 往负值增大,可以得到如图 4-6b 所示的一族漏极特性曲线。注意,随着 $V_{GS}$ 变为更大的负值,$I_D$减小,因为沟道变窄。也可以看到对于每一组 $V_{GS}$ ,JFET 在小于 $V_P$ 的 $V_{DS}$ 值下达到夹断状态(恒流开始的位置)。由此可见,$V_{GS}$可以控制漏极电流的大小。

4.2.6截止电压

使得 $I_D$ 的值接近于 0 的 $V_{GS}$ 称为截止电压,记为 $V_{GS(off)}$, JFET 必须工作在$V_{GS}=0V$ 和 $V_{GS(off)}$ 之间.随着栅源电压在此范围内变化, $I_D$ 最大可达到 $I_{DSS}$ ,最小达到接近于零.

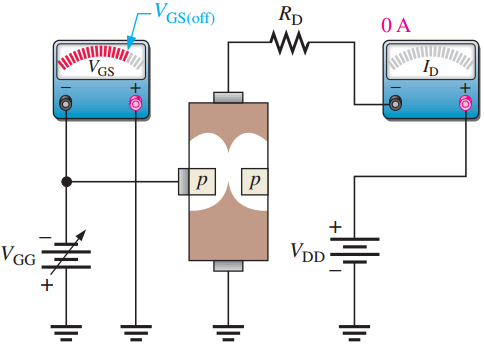

如前所述,对 n 沟道 JFET 而言,$V_{GS}$ 越往负值变大,恒流区中的 $I_D$ 值就越小。当 $V_{GS}$ 是一个足够大的负值时, $I_D$ 减小到 0。这一截止效应的产生是由于耗尽区不断变宽,最终完全关闭沟道,如图 4-7 所示。

$$

图4-7~~~截止的 ~JFET

$$

$$

图4-7~~~截止的 ~JFET

$$

4.2.7夹断和截止的比较

夹断电压在漏极特性中测量得到。对 n 沟道器件而言,夹断电压为正,是当 $V_{GS}=0V$ 时漏极电流变为恒定时的 $V_{DS}$。截止电压也可以在漏极特性中测量得到,是使得漏极电流变为零时的栅源电压,为负值。

$V_{GS(off)}$ 和 $V_P$ 始终大小相等,但符号相反。数据手册通常会给出 $V_{GS(off)}$ 或 $V_P$ 的值,但不会同时给出。但是,一旦知道其中一个,就能得到另一个。例如,如果 $V_{GS(off)}=-5V$,则$V_P=+5V$。

4.2.8 JFET 跨导曲线

描述电路的一种有用方式是给出输出和输人之间的关系,如1.4节中对放大器所做的一样。这一特性称为传输曲线。

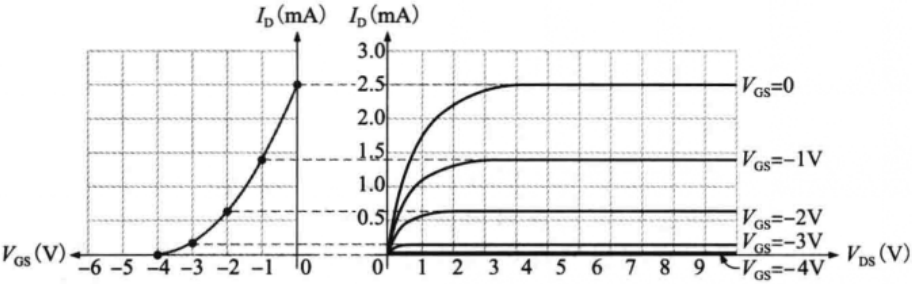

因为 JFET 由输人端(栅极)的负电压控制,并且输出是漏极电流,所以传输曲线是 $I_D$ 关于 $V_{GS}$ 的函数,其中 $I_D$ 对应 y 轴, $V_{GS}$ 对应 x 轴。当输出单位(mA)除以输人单位(V)时,结果是电导单位(mS)。可以将输入端传输到输出端的电压看成电沉,囚此在电导前面加上前缀“跨”形成跨导这个词语。跨导曲线是 FET 的输出特性( $I_D$ 对 $V_{GS}$ )曲线。在数据手册中一般以 $g_m$ 或者 $y_{fs}$ 来给出跨导。

$$

a)跨导曲线 ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)漏极曲线

$$

$$

a)跨导曲线 ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)漏极曲线

$$

$$ 图4-9~~MPF102 n沟道JFET的典型特性曲线 $$

n 沟道 JFET 的典型跨导曲线如图 4-9a 所示。一般来讲,所有类型的 FET 都有相同形状的跨导曲线。其中,曲线是 MPF102的典型曲线,这是一种通用的 n 沟道 JFET。

跨导特性与图 4-9b 所示的漏极特性直接相关。注意,这两条曲线都有相同的纵坐标 $I_D$。跨导是一个交流参数,其值可在曲线的任何点上通过漏极电流的变化除以栅源电压的变化得到。

$$

g_m=\frac{△I_D}{△V_{GS}}

$$

此式可写成交流形式为:

$$

g_m=\frac{I_d}{V_{gs}}~~~(4-1)

$$

跨导特性曲线并不是一条直线,这表明输出电流和输入电压间的关系是非线性的。这非常重要: FET 具有非线性的跨导曲线。这意味着 FET 可能会造成输入信号的失真。失真并不总是负面的,例如,在射频混频器中,JFET 因为失真特性反而较 BJT 有优势。然而,也有一些 JFET(例如 2N4339)通过几何设计使得失真最小,以便用于音频处理。此外,设计者也能通过保持较小的信号幅度(小于约 100mV)来减小失真。还有其他设计方法(如系统例子4-2中所使用的偏置方法)也用来减小失真。

4.2.9 JFET 输入电阻和电容

已经知道,pn 结在反向偏置时具有很高的电阻, 而 JFET 工作时栅源结反向偏置,因此栅极的输入电阻很大。这是 JFET 与 BJT 相比的一个主要优势,因为后者的发射结正向偏置。

JFET 的数据手册通常会通过给出特定栅源电压下的栅极反向电流 $I_{GSS}$ 来指明输入电阻。输入电阻可由下面的公式计算,其中竖线表示绝对值。 $$ R_{IN}=|\frac{V_{GS}}{I_{GSS}}|~~~~(4-2) $$ 例如,2N5457 的数据手册给出在 25℃,$V_{GS}=-15V$ 时,$I_{GSS}$ 最大值为 -1nA。用上述值可以计算得到输入电阻为 $$ R_{IN}=|\frac{V_{GS}}{I_{GSS}}|=\frac{15V}{1nA}=15G\Omega $$ 从结果可以看出,该 JFET 的输入电阻非常高。但是,随着温度升高,$R_{IN}$ 会明显下降(如例子4-3所示)。

输入端反向偏置的 pn 结的高电阻与反向偏置的二极管相关,但这也意味着 JFET 通常会有比 BJT 更大的输人电容值。已经知道反向偏置的 pn 结相当于一个电容,其电容值取决于反偏电压的大小(见2.8节)。JFET 的输入电容 $C_{iss}$ 比 BJT 的要高,因为其 pn 结反向偏置。例如,在 $V_{GS}=0V$ 时 2N5457 的 $C_{iss}$ 最大为 7pF。