虽然 BJT 和 JFET 都能用于开关电路,但 MOSFET 是目前大多数开关应用的首选器件。 MOSFET 具有很低的导通电阻,非常高的断开电阻,很快的切换时间,因此它是极好的开关器件。有两种基本类型的 MOSFET 开关电路:模拟和数字。本节将介绍数字和模拟 MOSFET 开关电路。

学完本节后,你应该掌握以下内容:

- 描述如何将 MOSFET 用于模拟和数字开关电路中

- 解释如何让 MOSFET 像开关一样工作

- 描述 MOSFET 模拟开关

- 讨论模拟开关应用

- 描述开关电容电路

- 描述 MOSFET 如何在数字开关电路中应用

- 讨论互补 MOS(CMOS) 逻辑

- 解释几种 CMOS数字门的工作原理

- 讨论几种功率 MOSFET 结构

4.7.1 MOSFET 开关工作原理

$$

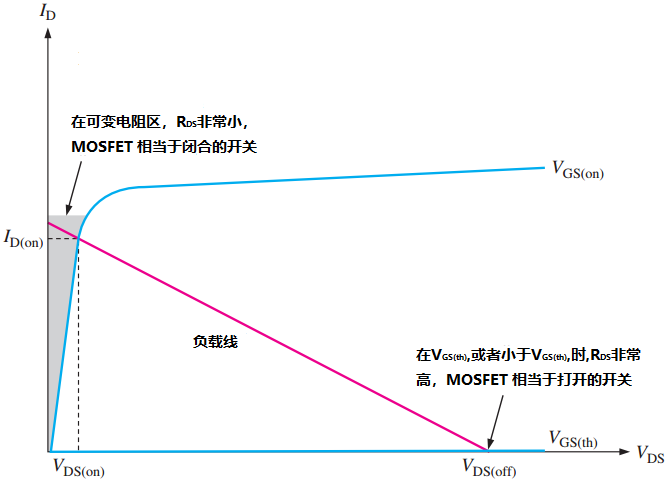

图4-52~~~在负载线上的开关工作

$$

通常将 E-MOSFET 用于开关应用,因为其具有阈值特性,$V_{GS(th)}$。当栅源电压小于阈值时,MOSFET 处于关闭状态。当栅源电压大于阈值时, MOSFET 导通。当 $V_{GS}$ 在 $V_{GS(th)}$ 与 $V_{GS(on)}$ 之间变化时, MOSFET 就以开关方式工作,如图4-52所示。在关闭状态, $V_{GS}$ < $V_{GS(th)}$ ,器件工作在负载线的下端,相当于一个打开的开关(非常高的 $R_{DS}$)。当$V_{GS}$ 足够大于 $V_{GS(th)}$ 时,器件工作在负载线上端的可变电阻区,相当于一个闭合的开关(非常低的 $R_{DS}$)。

$$

图4-52~~~在负载线上的开关工作

$$

通常将 E-MOSFET 用于开关应用,因为其具有阈值特性,$V_{GS(th)}$。当栅源电压小于阈值时,MOSFET 处于关闭状态。当栅源电压大于阈值时, MOSFET 导通。当 $V_{GS}$ 在 $V_{GS(th)}$ 与 $V_{GS(on)}$ 之间变化时, MOSFET 就以开关方式工作,如图4-52所示。在关闭状态, $V_{GS}$ < $V_{GS(th)}$ ,器件工作在负载线的下端,相当于一个打开的开关(非常高的 $R_{DS}$)。当$V_{GS}$ 足够大于 $V_{GS(th)}$ 时,器件工作在负载线上端的可变电阻区,相当于一个闭合的开关(非常低的 $R_{DS}$)。

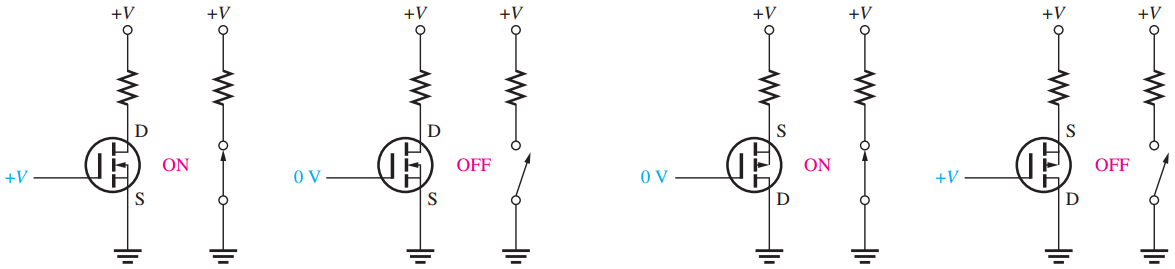

$$ a) ~n沟道MOSFET和等效开关~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b) ~p沟道MOSFET和等效开关 $$

$$ 图4-53~~~MOSFET开关 $$ 理想开关参考图4-53a。当 n 沟道 MOSFET 的栅极电压为 +V时,栅极电压相对于源极电压为正,并比源极电压高超过 $V_{GS(th)}$ 的值。此时,MOSFET 导通,漏极与源极之间相当于闭合开关。当栅极电压为零时,栅源电压为零。此时 MOSFET 处于关闭状态,漏极与源极之间的相当于打开的开关。

参考图4-53b。当 p 沟道MOSFET的栅极电压为 0 时,栅极电压相对于源极电压为负,并且两者绝对差值超过 $V_{GS(th)}$。MOSFET 导通,漏极与源极之间相当于闭合的开关。当栅极电压为 +V 时,栅源电压为零。MOSFET 处于关闭状态,漏极与源极之间相当于打开的开关。

4.7.2模拟开关

MOSFET 通常用于模拟信号开关。一般来讲,一个加到漏极上的信号可以通过栅极上的电压来接通或断开与源极的相连。主要限制在于源极的信号大小不能导致栅源电压小于 $V_{GS(th)}$ .

$$

a)~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)

$$

$$

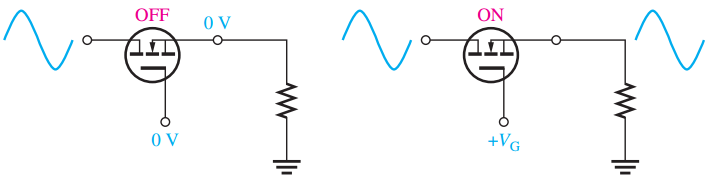

图4-54 ~~~n沟道MOSFET模拟开关的工作原理

$$

一个基本的 n 沟道 MOSFET 模拟开关如图4-54所示。当由于正 $V_{GS}$ 使得 MOSFET导通时,漏极上的信号连接到源极,当 $V_{GS}$ 为 0 时,漏极上的信号与源极断开,如图4-54所示。

$$

a)~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)

$$

$$

图4-54 ~~~n沟道MOSFET模拟开关的工作原理

$$

一个基本的 n 沟道 MOSFET 模拟开关如图4-54所示。当由于正 $V_{GS}$ 使得 MOSFET导通时,漏极上的信号连接到源极,当 $V_{GS}$ 为 0 时,漏极上的信号与源极断开,如图4-54所示。

$$

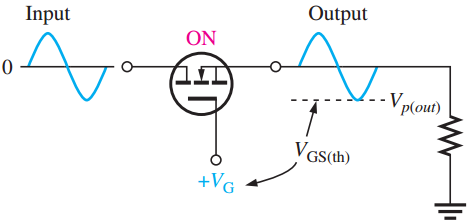

图4-55~~~信号幅度被V_{GS(th)}限制

$$

当模拟开关导通时,如图4-55所示,在信号的负峰值栅源电压有最小值。 $V_G$ 与 $V_{p(out)}$ 的差值是信号为负峰值瞬时时刻的栅源电压,它必须等于或大于 $V_{GS(th)}$ 以保证 MOSFET 处于导通工作。

$$

V_{GS}=V_G-V_{p(out)}\geq V_{GS(th)}

$$

$$

图4-55~~~信号幅度被V_{GS(th)}限制

$$

当模拟开关导通时,如图4-55所示,在信号的负峰值栅源电压有最小值。 $V_G$ 与 $V_{p(out)}$ 的差值是信号为负峰值瞬时时刻的栅源电压,它必须等于或大于 $V_{GS(th)}$ 以保证 MOSFET 处于导通工作。

$$

V_{GS}=V_G-V_{p(out)}\geq V_{GS(th)}

$$

4.7.3模拟开关应用

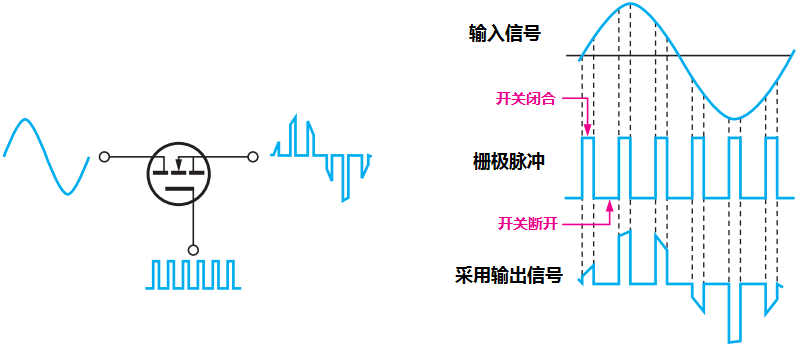

采样电路模拟开关的应用之一是模数转换。模拟开关用于采样保持电路,来以特定速率对输入信号进行采样。然后每个采样信号值暂时存储在电容中,直到被一个模-数转换器(ADC)转换成数字编码。为了实现这个目标,MOSFET 通过加在栅极上的脉冲在输入信号的一个周期内的短时间内导通。基本工作原理如图4-56所示,为清晰起见,其中只显示了几个采样。

$$

a)电路行为~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)波形图

$$

$$

a)电路行为~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)波形图

$$

$$

图4-56~~~模拟开关作为采样电路

$$

信号采样以及能从采样的信号中重构的最小速率必须大于信号最大频率的两倍。这最小采样频率称为奈奎斯特频率。

$$

f_{sample(min)}>2f_{signal(max)}

$$

当栅极脉冲为高电平时,开关闭合,该脉冲期间的一小部分输入波形出现在输出上。当栅极脉冲为0V时,开关断开,输出也为0V。

$$

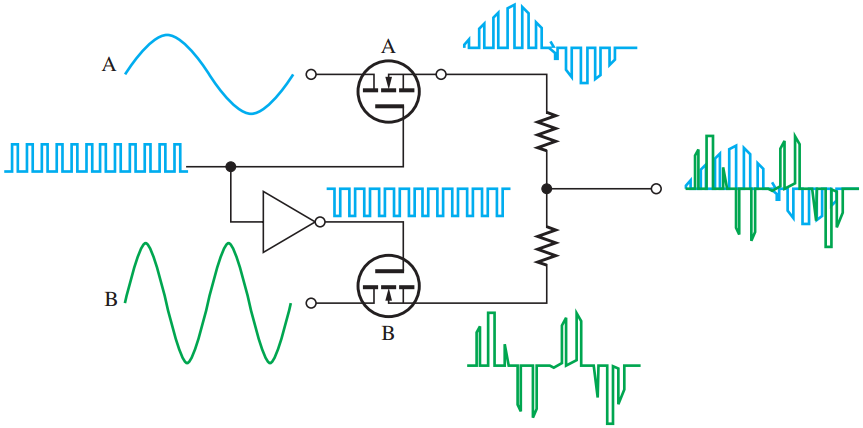

图4-57~~~模拟复用器交替采样两个信号,并在单一输出线上实现交错传输

$$

模拟复用器模 拟复用器用于需要将两路或多路信号传输到同一目标的应用中。例如,图4-57所示为一双通道模拟采样复用器。两个 MOSFET 交替导通和截止,这样信号采样先后连接到输出。脉冲信号加到开关 A 的栅极,反相脉冲信号加到开关 B 的栅极。一个称为反相器的数字电路用来实现这个目标。当脉冲为高电平时,开关 A 闭合,开关 B 断开。当脉冲为低电平时,开关 B 闭合,开关 A 断开。这称为时分复用,因为脉冲为高电平的时间间隔内,信号 A 出现在输出,脉冲为低电平的时间间隔内,信号 B 出现在输出。也就是说,这两个信号在时间上交错以便在一条线上进行传输。

$$

图4-57~~~模拟复用器交替采样两个信号,并在单一输出线上实现交错传输

$$

模拟复用器模 拟复用器用于需要将两路或多路信号传输到同一目标的应用中。例如,图4-57所示为一双通道模拟采样复用器。两个 MOSFET 交替导通和截止,这样信号采样先后连接到输出。脉冲信号加到开关 A 的栅极,反相脉冲信号加到开关 B 的栅极。一个称为反相器的数字电路用来实现这个目标。当脉冲为高电平时,开关 A 闭合,开关 B 断开。当脉冲为低电平时,开关 B 闭合,开关 A 断开。这称为时分复用,因为脉冲为高电平的时间间隔内,信号 A 出现在输出,脉冲为低电平的时间间隔内,信号 B 出现在输出。也就是说,这两个信号在时间上交错以便在一条线上进行传输。

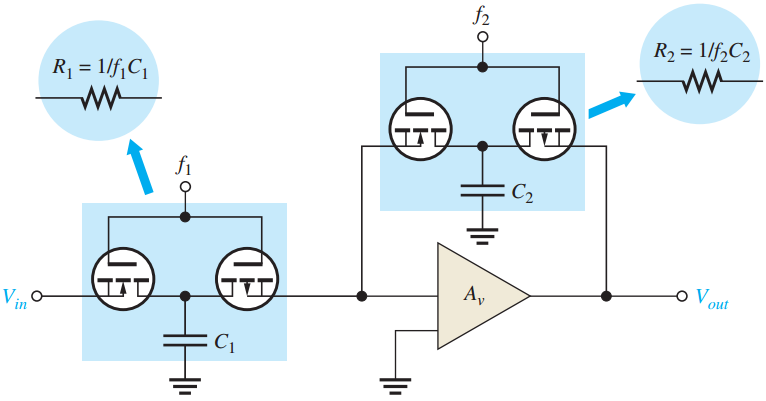

开关电容电路 MOSFET 的另一应用是开关电容电路,它通常用于称为模拟信号处理器的集成电路可编程模拟器件中。因为电容在集成电路中比电阻更容易实现,所以它用来模拟电阻。此外,电容在芯片上占据的空间比IC电阻也要少,也不会消耗功率。许多类型的模拟电路利用电阻来确定电压增益和其他特性,通过开关电容模拟电阻,可以实现模拟电路的动态编程。

$$

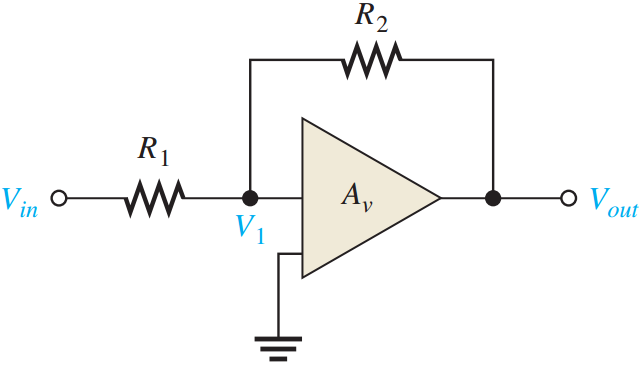

图4-58~~~一种IC放大器

$$

$$

图4-58~~~一种IC放大器

$$

例如,在后面会学到的一种IC放大器电路中,需要两个外部电阻,如图4-58所示。这些电阻值确定了放大器的电压增益为 $A_v=R_2/R_1$。

$$

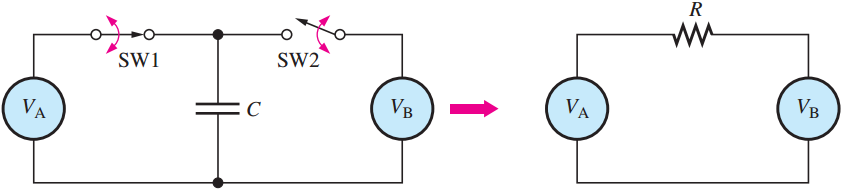

图4-59~~~开关电容模拟电阻

$$

$$

图4-59~~~开关电容模拟电阻

$$

利用机械开关类推(把 MOSFET实际上当成开关),可以使用开关电容来模拟一个电阻,如图4-59所示。开关 1 和开关 2 以一定频率交替闭合和断开,来对电容进行充电或放电,这一过程取决于电压源的值。对于图4-58中的 $R_1,V_{in}$和 $V_1$ 分别用 $V_A$ 和 $V_B$ 表示。对于 $R_2,V_1$和 $V_{out}$ 分别用 $V_A$ 和 $V_B$ 表示。

可以看出电容模拟电阻的阻值取决于开关闭合断开的频率和电容容值。

$$

R=\frac{1}{fC}

$$

通过改变频率,可以改变有效阻值。

$$

图4-60~~~图4-58中IC放大器,其中电阻用开关电容电路代替

$$

$$

图4-60~~~图4-58中IC放大器,其中电阻用开关电容电路代替

$$

互补 E-MOSFET 和电容可以代替放大器中的电阻,如图4-60所示。当 $Q_1$ 导通时, $Q_2$ 截止, 反之亦然。选取合适的 $f_1$ 与 $C_1$ 来得到所需的 $R_1$ 值。同样,$f_2$ 和 $C_2$ 提供所需的 $R_2$ 值。要编程改变放大器的增益,改变频率就可以。

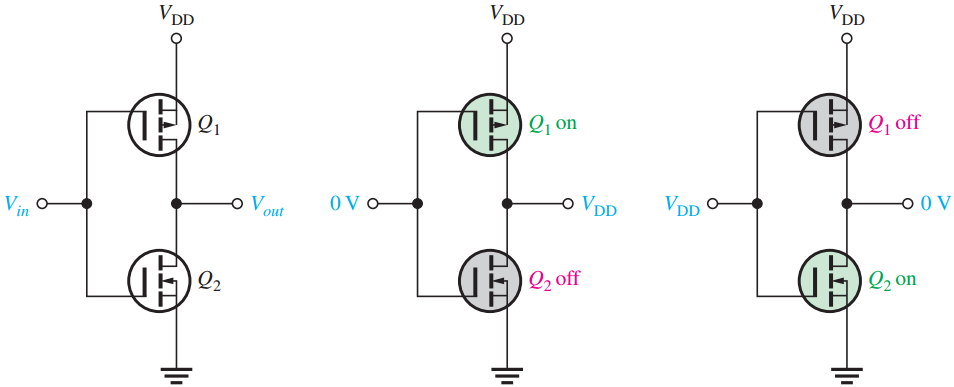

4.7.4 CMOS:数字开关应用

$$

a)~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~c)

$$

$$

图4-61 ~~~CMOS反相器原理

$$

CMOS 将 n 沟道与 p 沟道 E-MOSFET 以串联方式组合在一起,如图4-61a所示。栅极上的输入电压为 0V 或者 $V_{DD}$。注意, $V_{DD}$ 和地都连接到两个晶体管的源极。为避免混淆,规定 $V_{DD}$ 为正电压,连接到 p 沟道器件的源极。当 $V_{in}=0V$ 时,$Q_1$ 导通,$Q_2$ 截止,如图4-61b所示。由于 $Q_1$ 相当于闭合的开关,因此输出约为 $V_{DD}$。当 $V_{in}=V_{DD}$ 时,$Q_2$ 导通,$Q_1$ 截止,如图4-61c所示。由于 $Q_2$ 相当于闭合的开关,因此输出本质上为接地(0V)。

$$

a)~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~b)~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~c)

$$

$$

图4-61 ~~~CMOS反相器原理

$$

CMOS 将 n 沟道与 p 沟道 E-MOSFET 以串联方式组合在一起,如图4-61a所示。栅极上的输入电压为 0V 或者 $V_{DD}$。注意, $V_{DD}$ 和地都连接到两个晶体管的源极。为避免混淆,规定 $V_{DD}$ 为正电压,连接到 p 沟道器件的源极。当 $V_{in}=0V$ 时,$Q_1$ 导通,$Q_2$ 截止,如图4-61b所示。由于 $Q_1$ 相当于闭合的开关,因此输出约为 $V_{DD}$。当 $V_{in}=V_{DD}$ 时,$Q_2$ 导通,$Q_1$ 截止,如图4-61c所示。由于 $Q_2$ 相当于闭合的开关,因此输出本质上为接地(0V)。

CMOS的主要优点是它的直流消耗功率非常小。由于两个 MOSFET串联,且其中一个始终处于断开状态,因此在静止状态时,直流电源中基本上没有电流流过。当 MOSFET 开关时,只有在非常短的时间内会有电流,因为只有在这个极短的状态转变的时间间隔内,两个晶体管会同时导通,

反相器 注意,图4-61所示的电路实际上会使输入反相,因为当输人为 0V 或者低电平时,输出为 $V_{DD}$ 或者高电平。当输入为 $V_{DD}$ 或者高电平时,输出为 0V 或低电平。因此,该电路在数字电子中称为反相器。

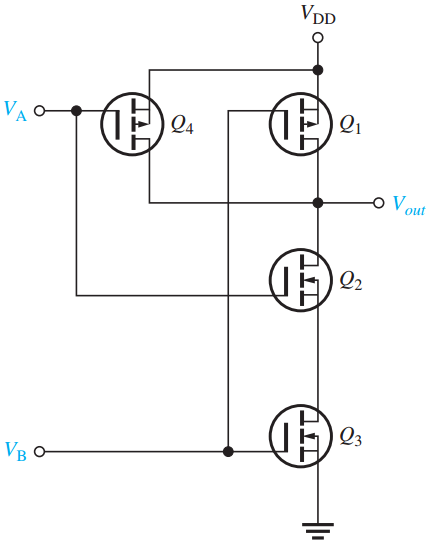

$$

a)

$$

$$

a)

$$

$$ 图4-62~~~CMOS 与非门工作原理 $$

与非门 在图4-62a中,在 CMOS 对的基础上增加了两个额外的 MOSFET 和第二个输入,得到一个称为与非门的数字电路。$Q_4$ 与 $Q_1$ 并联,$Q_3$ 与 $Q_2$ 串联。当两个输入 $V_A$ 和 $V_B$ 均为 0 时,$Q_1$ 和 $Q_4$ 导通,而 $Q_2$ 和 $Q_3$ 截止,使得 $V_{out}=V_{DD}$。当两个输入均等于 $V_{DD}$ 时,$Q_1$ 和 $Q_4$ 截止,而 $Q_2$ 和 $Q_3$ 导通,使得$V_{out}=0$。可以验证,当两个输入不同,即一端为 $V_{DD}$ 另一端为0时,输出等于 $V_{DD}$。工作状态可总结为如图4-62b中的表,并表述如下:

| $V_A$ | $V_B$ | $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $V_{out}$ |

|---|---|---|---|---|---|---|

| 0 | 0 | 导通 | 截止 | 截止 | 导通 | $V_{DD}$ |

| 0 | $V_{DD}$ | 截止 | 截止 | 截止 | 导通 | $V_{DD}$ |

| $V_{DD}$ | 0 | 导通 | 截止 | 截止 | 截止 | $V_{DD}$ |

| $V_{DD}$ | $V_{DD}$ | 截止 | 导通 | 导通 | 截止 | 0 |

当 $V_A$ 与 $V_B$ 为高电平时,输出为低电平; 否则,输出为高电平。

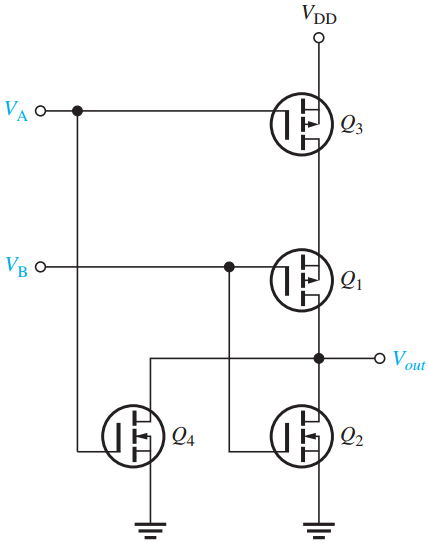

$$

图4-63~~~CMOS或非门工作原理

$$

$$

图4-63~~~CMOS或非门工作原理

$$

或非门 在图4-63a中,在 CMOS 对的基础上增加了两个额外的 MOSFET 和第二个输入端,得到一个称为或非门的数字电路。$Q_4$ 与 $Q_2$ 并联,$Q_3$ 与 $Q_1$ 串联。当两个输入 $V_A $和 $V_B$均为0时, $Q_1$和 $Q_3$导通,而 $Q_2$和 $Q_4$截止,使得 $V_{out} =V_{DD}$。当两个输入均等于 $V_{DD}$ 时,$Q_1$ 和 $Q_3$ 截止,而 $Q_2$ 和 $Q_4$ 导通,使得 $V_{out}=0 $。可以验证,当输入不同,即一端为 $V_{DD}$ 另一端为 0 时,输出等于 0。工作状态可总结为图4-63b中的表,并表述如下:

| $V_A$ | $V_B$ | $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $V_{out}$ |

|---|---|---|---|---|---|---|

| 0 | 0 | 导通 | 截止 | 导通 | 截止 | $V_{DD}$ |

| 0 | $V_{DD}$ | 截止 | 导通 | 导通 | 截止 | 0 |

| $V_{DD}$ | 0 | 导通 | 截止 | 导通 | 截止 | 0 |

| $V_{DD}$ | $V_{DD}$ | 截止 | 导通 | 截止 | 导通 | 0 |

当 $V_A$ 或 $V_B$ 或二者均为高电平时,输出为低电平; 否则,输出为高电平。

4.7.5 功率开关应用中的 MOSFET

在大多数高功率开关应用中,功率 MOSFET 大量代替了 BJT,其中原因很多。MOSFET 截止更快,不需要驱动电流,导通电阻更低(消耗功率更小),并且具有正温度系数——变热时电阻增大。这意味着与 BJT(具有负温度系数)相比,MOSFET 更不容易发生热漂移。功率 MOSFET 用于电机控制,直流到交流和直流到直流转换,负载开关,或其他需要高功率和精确数字控制的任何场合。例如,2SK4124的额定漏源电压($V_{DSS}$)为500V,额定连续漏极电流为20A,脉冲漏极电流60A。若安装合适的散热器,则额定功率可以达到170W。

4.7.6 功率 MOSFET 结构

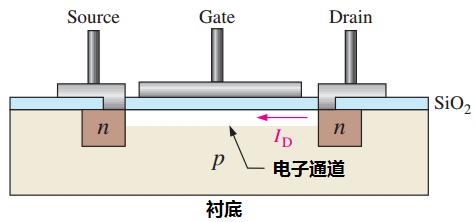

$$

图4-64~~~传统E-MOSFET结构横截面。白色区域为沟道

$$

传统的增强型 MOSFET 具有薄且长的横向沟道,如图4-64的结构图所示。其中

$$

图4-64~~~传统E-MOSFET结构横截面。白色区域为沟道

$$

传统的增强型 MOSFET 具有薄且长的横向沟道,如图4-64的结构图所示。其中红色箭头表示多数载流子从源极到漏极的移动。这使得漏源电阻相当高,并限制了 E-MOSFET 的低功耗应用。当栅极电压为正时,在源极和漏极之间靠近栅极处形成沟道,如图4-64所示。

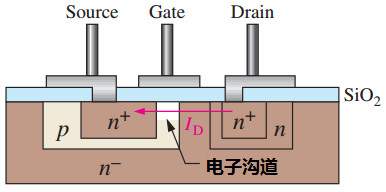

横向扩散 MOSFET(LDMOSFET) LDMOSFET 具有横向沟道结构,是一种用于功率应用的增强型 MOSFET。与传统 E-MOSFET 相比,器件在漏极和源极间的沟道更短。沟道更短使得电阻更小,因此允许更大的电压和电流。

$$

图4-65 ~~~LDMOSFET横向沟道结构横截面

$$

图4-65给出了 LDMOSFET 的基本结构。当栅极为正时,在轻掺杂的源极和 $n^-$ 区域之间的 p 层内会感应出一个很短的 n 沟道。多数载流子通过 n 区域和感应沟道从源极移动到漏极,如图4-65所示。

$$

图4-65 ~~~LDMOSFET横向沟道结构横截面

$$

图4-65给出了 LDMOSFET 的基本结构。当栅极为正时,在轻掺杂的源极和 $n^-$ 区域之间的 p 层内会感应出一个很短的 n 沟道。多数载流子通过 n 区域和感应沟道从源极移动到漏极,如图4-65所示。

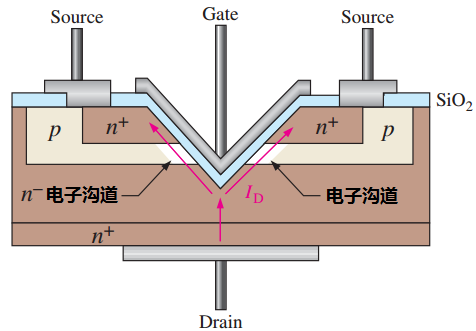

VMOSFET V形槽MOSFET是另一种用于更高功率的E-MOSFET,它利用垂直沟道结构,实现了漏极与源极之间更短、更宽且电阻更低的沟道。这样的沟道能允许更大的电流,从而允许更大的功耗。频率响应也有所改善。

$$

图4-66~~~VMOSFET垂直沟道结构的横截面

$$

VMOSFET 顶部有两个源极,一个栅极,底部有一个漏极,如图4-66 所示。在漏极($n^+$ 衬底,其中 $n^+$ 意味着比 $n^-$ 更高的掺杂)与源极之间的 V 形槽的两侧垂直感应出沟道。沟道长度由层的厚度决定,而厚度由掺杂浓度和扩散时间决定。

$$

图4-66~~~VMOSFET垂直沟道结构的横截面

$$

VMOSFET 顶部有两个源极,一个栅极,底部有一个漏极,如图4-66 所示。在漏极($n^+$ 衬底,其中 $n^+$ 意味着比 $n^-$ 更高的掺杂)与源极之间的 V 形槽的两侧垂直感应出沟道。沟道长度由层的厚度决定,而厚度由掺杂浓度和扩散时间决定。

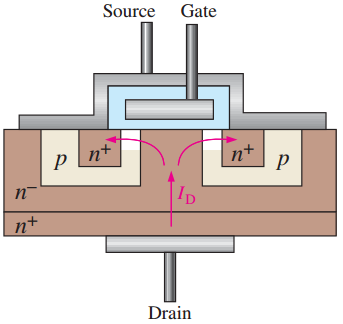

$$

图4-67~~~TMOSFET垂直沟道结构的横截面

$$

TMOSFET TMOSFET的垂直沟道结构如图4-67所示。栅极结构被嵌入到二氧化硅层中,源极覆盖了整个表面区域。漏极位于底部。TMOSFET比VMOSFET具有更高的封装密度,同时保持了短垂直沟道的优点。

$$

图4-67~~~TMOSFET垂直沟道结构的横截面

$$

TMOSFET TMOSFET的垂直沟道结构如图4-67所示。栅极结构被嵌入到二氧化硅层中,源极覆盖了整个表面区域。漏极位于底部。TMOSFET比VMOSFET具有更高的封装密度,同时保持了短垂直沟道的优点。